# THE BOOK OF I<sup>2</sup>C

A GUIDE FOR ADVENTURERS

# THE BOOK OF I<sup>2</sup>C

# THE BOOK OF I<sup>2</sup>C

# A Guide for Adventurers

# by Randall Hyde

San Francisco

#### THE BOOK OF I<sup>2</sup>C. Copyright © 2023 by Randall Hyde.

All rights reserved. No part of this work may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage or retrieval system, without the prior written permission of the copyright owner and the publisher.

#### First printing

29 28 27 26 25 1 2 3 4 5

ISBN-13: 978-1-7185-0246-8 (print) ISBN-13: 978-1-7185-0247-5 (ebook)

Published by No Starch Press<sup>®</sup>, Inc. 245 8th Street, San Francisco, CA 94103 phone: +1.415.863.9900 www.nostarch.com; info@nostarch.com

Publisher: William Pollock Managing Editor: Jill Franklin

Production Manager: Rachel Monaghan

Production Editor: Miles Bond

Developmental Editors: Abigail Schott-Rosenfield, Athabasca Witschi, and Jill Franklin

Cover Illustrator: Gina Redman Interior Design: Octopod Studios Technical Reviewer: Anthony Tribelli

Copyeditor: Kim Wimpsett

Compositor: Happenstance Type-O-Rama

Proofreader: Sadie Barry

Library of Congress Cataloging-in-Publication Data

Names: Hyde, Randall, author.

Title: The book of I<sup>2</sup>C : a guide for adventurers / Randall Hyde.

Description: San Francisco : No Starch Press, [2022] | Includes index. |

Identifiers: LCCN 2022018708 (print) | LCCN 2022018709 (ebook) | ISBN 9781718502468 (print) |

ISBN 9781718502475 (ebook)

Subjects: LCSH: I2C (Computer bus) | Microcomputers--Programming. | Microcontrollers--Programming.

Classification: LCC TK7895.B87 H94 2022 (print) | LCC TK7895.B87 (ebook)

DDC 621.39/16--dc23/eng/20220627

LC record available at https://lccn.loc.gov/2022018708

LC ebook record available at https://lccn.loc.gov/2022018709

For customer service inquiries, please contact info@nostarch.com. For information on distribution, bulk sales, corporate sales, or translations: sales@nostarch.com. For permission to translate this work: rights@nostarch.com. To report counterfeit copies or piracy: counterfeit@nostarch.com.

No Starch Press and the No Starch Press iron logo are registered trademarks of No Starch Press, Inc. Other product and company names mentioned herein may be the trademarks of their respective owners. Rather than use a trademark symbol with every occurrence of a trademarked name, we are using the names only in an editorial fashion and to the benefit of the trademark owner, with no intention of infringement of the trademark.

The information in this book is distributed on an "As Is" basis, without warranty. While every precaution has been taken in the preparation of this work, neither the author nor No Starch Press, Inc. shall have any liability to any person or entity with respect to any loss or damage caused or alleged to be caused directly or indirectly by the information contained in it.

This book is dedicated to Limor "Lady Ada" Fried of Adafruit and Nathan Seidle of SparkFun.

Without these two great companies,

I never would have thought about creating a book such as this one.

#### **About the Author**

Randall Hyde is the author of *The Art of 64-Bit Assembly; The Art of Assembly Language*; and *Write Great Code*, Volumes 1, 2, and 3 (all from No Starch Press); as well as *Using 6502 Assembly Language and P-Source* (Datamost). He is also the coauthor of *Microsoft Macro Assembler 6.0 Bible* (The Waite Group). Over the past 40 years, Hyde has worked as an embedded software and hardware engineer developing instrumentation for nuclear reactors, traffic control systems, and other consumer electronics devices. He has also taught computer science at California State Polytechnic University, Pomona, and at the University of California, Riverside. His website is *https://www.randallhyde.com*.

### **About the Technical Reviewer**

Anthony Tribelli has more than 35 years of experience in software development. This experience ranges, among other things, from embedded device kernels to molecular modeling and visualization to video games. The latter includes 10 years at Blizzard Entertainment. He is currently a software development consultant and is privately developing applications utilizing computer vision.

# **BRIEF CONTENTS**

| Acknowledgments                                                             | xvii |

|-----------------------------------------------------------------------------|------|

| Introduction                                                                | xix  |

| PART I: LOW-LEVEL PROTOCOLS AND HARDWARE                                    | 1    |

| Chapter 1: I <sup>2</sup> C Low-Level Hardware                              | 3    |

| Chapter 2: I <sup>2</sup> C Protocol                                        | 15   |

| Chapter 3: A Software Implementation of the I <sup>2</sup> C Bus            | 31   |

| Chapter 4: Tools for Analyzing and Debugging I <sup>2</sup> C Transmissions | 67   |

| Chapter 5: I <sup>2</sup> C Variants                                        | 81   |

| PART II: HARDWARE IMPLEMENTATIONS                                           |      |

| Chapter 6: $I^2$ C on Common Single-Board Computers                         | 93   |

| Chapter 7: I <sup>2</sup> C on Vendor Buses                                 |      |

| PART III: PROGRAMMING THE I <sup>2</sup> C BUS                              | 129  |

| Chapter 8: Arduino I <sup>2</sup> C Programming                             | 131  |

| Chapter 9: Raspberry Pi (and Linux) I <sup>2</sup> C Programming            | 147  |

| Chapter 10: I <sup>2</sup> C Programming in Real-Time Operating Systems     | 175  |

| Chapter 11: Bare-Metal I <sup>2</sup> C Controller Programming              | 207  |

| PART IV: I <sup>2</sup> C PERIPHERAL PROGRAMMING EXAMPLES                   | 251  |

| Chapter 12: The TCA9548A I <sup>2</sup> C Bus Expander                      | 253  |

| Chapter 13: The MCP23017 and MCP23008 GPIO Expanders                        | 261  |

| Chapter 14: The ADS1015 and ADS1115 Analog-to-Digital Converters .          | 299  |

| Chapter 15: The MCP4725 Digital-to-Analog Converter                         | 341  |

| Chapter 16: Bare-Metal Peripheral Programming                               | 349  |

| Epilogue                                                      |

|---------------------------------------------------------------|

| Appendix A: The Adafruit I <sup>2</sup> C Address Compilation |

| Appendix B: Online Chapters                                   |

| Glossary                                                      |

| Index                                                         |

# **CONTENTS IN DETAIL**

| ACKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xvii                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xix                                                                           |

| PART I: LOW-LEVEL PROTOCOLS AND HARDWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                             |

| 1<br>I <sup>2</sup> C LOW-LEVEL HARDWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                             |

| 1.1 I <sup>2</sup> C Overview 1.2 Open-Drain (Open-Collector) Logic and Four-Wire Mode 1.3 I <sup>2</sup> C Signal Levels 1.3.1 Level Shifting 1.4 Choosing Pullup Resistor Sizes 1.5 Bus Capacitance and Pullup Resistor Values 1.5.1 What If the Bus Capacitance Is Too High? 1.6 I <sup>2</sup> C Bus Speeds 1.7 Multicontroller I <sup>2</sup> C Bus Clock Synchronization 1.8 Multicontroller I <sup>2</sup> C Bus Arbitration 1.9 Clock Stretching 1.10 Cross Talk 1.11 Chapter Summary | 5<br>7<br>8<br>9<br>9<br>10<br>12<br>13                                       |

| 2<br>I <sup>2</sup> C PROTOCOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19<br>.19<br>20<br>. 21<br>. 23<br>. 23<br>. 24<br>. 24<br>. 25<br>. 26<br>28 |

| 3          | SOFTWARE IMPLEMENTATION OF THE I <sup>2</sup> C BUS                   | 31       |

|------------|-----------------------------------------------------------------------|----------|

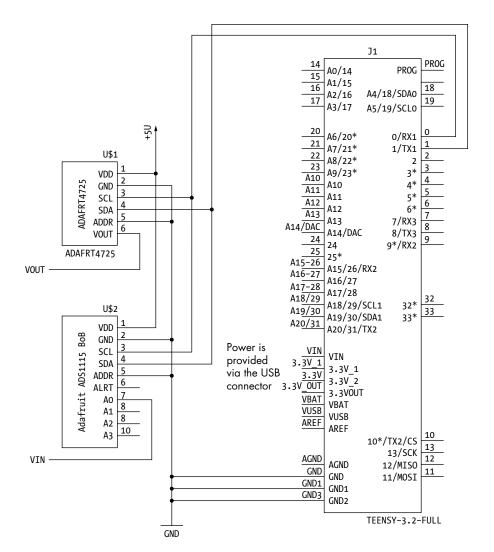

|            | A Software I <sup>2</sup> C Implementation on the Teensy 3.2          | -        |

| •          | 3.1.1 A Software-Based I <sup>2</sup> C Controller for the Teensy 3.2 | 32       |

|            | 3.1.2 A Software-Based I <sup>2</sup> C Peripheral for the Teensy 3.2 |          |

| 3.2        | Basic ATtiny84 and ATtiny85 Hardware                                  | 64       |

| 3.3        | 3.2.1 Atto84 Software-Based I <sup>2</sup> C Peripheral               |          |

|            | , , , , , , , , , , , , , , , , , , , ,                               |          |

| 4<br>TO    | OLS FOR ANALYZING AND DEBUGGING I <sup>2</sup> C TRANSMISSIONS        | 67       |

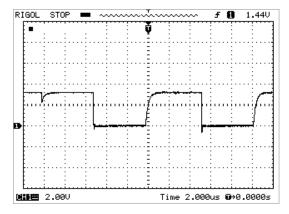

|            | Generic Hardware Testing and Debugging Tools                          |          |

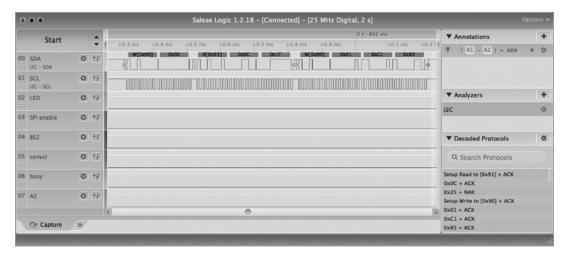

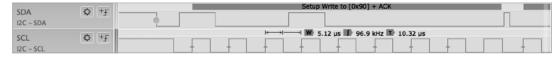

| 4.2        | Logic Analyzers                                                       | 70       |

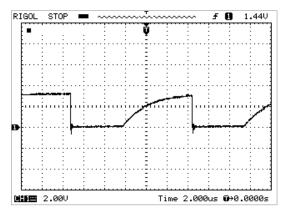

|            | The I <sup>2</sup> C Driver                                           |          |

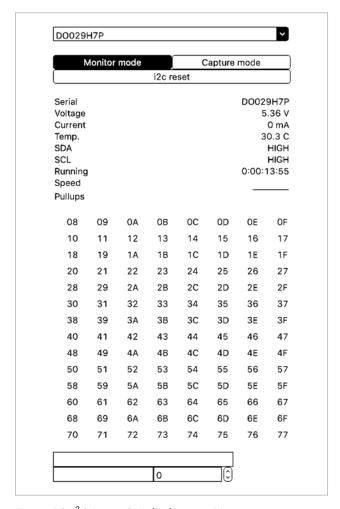

| 4.5        | The Saleae Logic Analyzers                                            | 75       |

|            | A Final Comment on I <sup>2</sup> C Monitors and Logic Analyzers      |          |

| 4./        | Chapter Summary                                                       | 70       |

| 5<br>12C   | VARIANTS                                                              | 81       |

|            |                                                                       |          |

| 5.1        | SMBus                                                                 | 82<br>82 |

|            | 5.1.2 SMBus Electrical Specifications                                 | 83       |

|            | 5.1.3 SMBus Reserved Addresses                                        | 83<br>84 |

|            | VESA DDC and E-DDC                                                    | 89       |

|            | ACCESS.bus                                                            |          |

|            | Chapter Summary                                                       |          |

|            |                                                                       |          |

| <b>D</b> 4 | ART II. IIARRAAART IAARI FAAFAITATIONIC                               | ^-       |

| P          | ART II: HARDWARE IMPLEMENTATIONS                                      | 91       |

| 6          |                                                                       |          |

|            | ON COMMON SINGLE-BOARD COMPUTERS                                      | 93       |

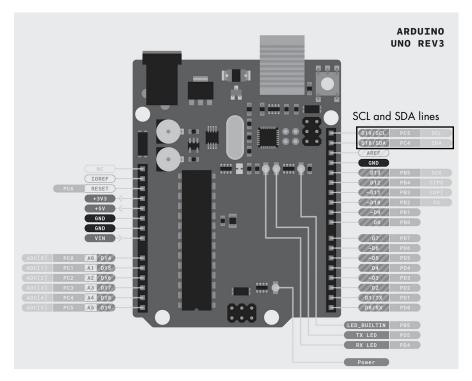

| 6.1        | The Arduino Family                                                    |          |

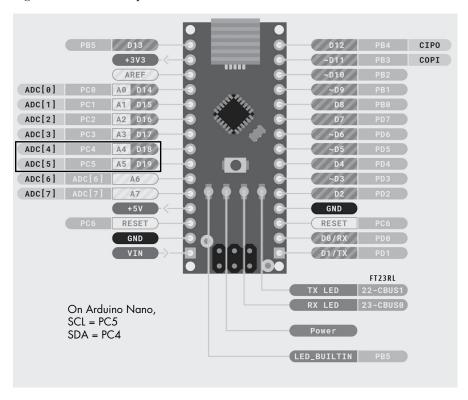

|            | 6.1.2 The Arduino Ono Keys and Leonardo                               |          |

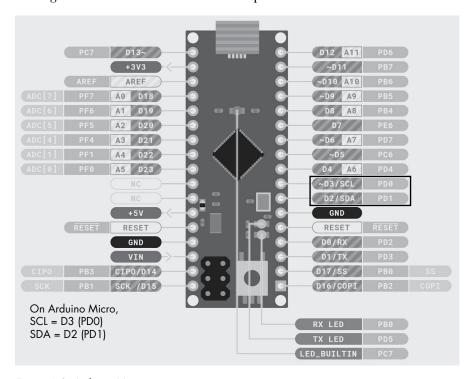

|            | 6.1.3 The Arduino Micro                                               |          |

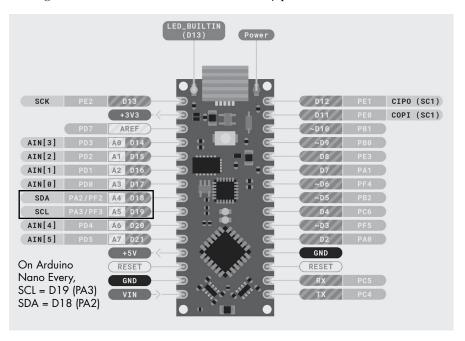

|            | 6.1.4 The Arduino Nano Every                                          | 98<br>98 |

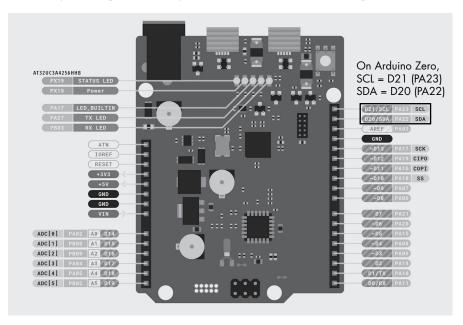

|            | 6.1.6 The Arduino Zero                                                | 100      |

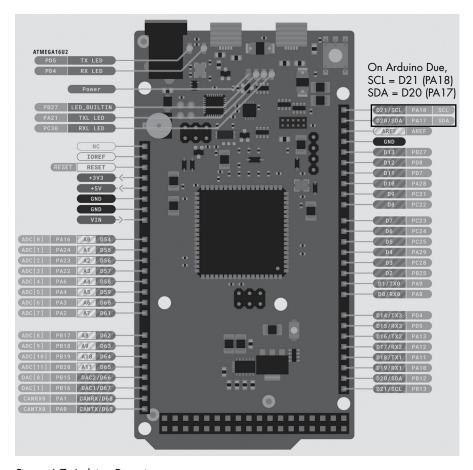

|            | 6.1.7 The Arduino Due                                                 |          |

| 6.2        | 6.1.8 Other Arduino-Brand Single-Board Computers                      |          |

|            | SparkFun Single-Board Computers                                       |          |

| <ul><li>6.4 The Teensy Family</li></ul>                                         |       |

|---------------------------------------------------------------------------------|-------|

| 6.6 The Raspherry Pi                                                            | 10.4  |

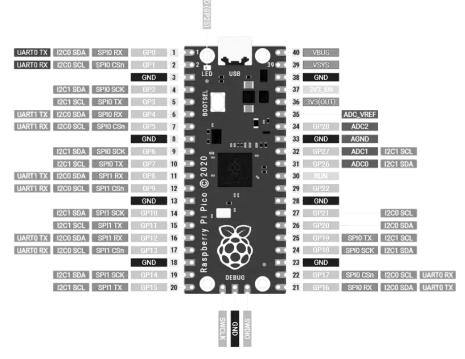

| 6.7 The Raspberry Pi Pico                                                       | 107   |

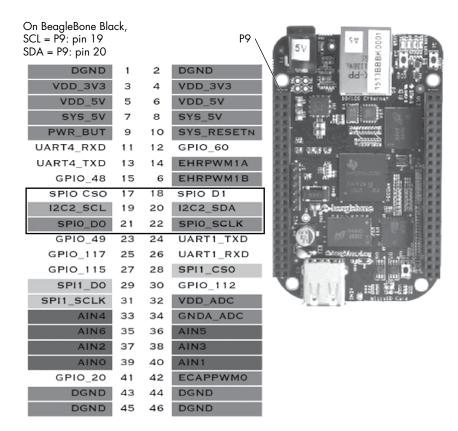

| 6.8 The BeagleBone Black                                                        | 108   |

| 6.9 The PINE A64 and ROCKPro64                                                  | 109   |

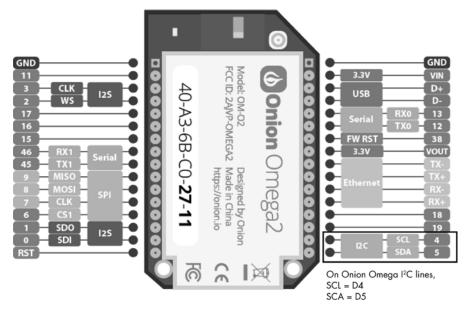

| 6.10 The Onion Omega                                                            | 109   |

| 6.11 The STM32 Single-Board Computer Family                                     |       |

| 6.11.1 STM32F767/Nucleo-144                                                     |       |

| 6.11.3 STM32 Boards Galore                                                      |       |

| 6.12 The NetBurner MOD54415                                                     |       |

| $6.13  \text{l}^2\text{C}$ on the Personal Computer                             | 112   |

| 6.14 Chapter Summary                                                            | 112   |

| 7                                                                               |       |

| I <sup>2</sup> C ON VENDOR BUSES                                                | 115   |

| 7.1 The Adafruit Feather Bus                                                    |       |

| 7.1.1 Feather Bus Pinouts                                                       |       |

| 7.1.2 $I^2C$ on the Feather Bus                                                 |       |

| 7.1.3 Multicontroller Operation                                                 |       |

| 7.1.4 redities and redities villigs                                             | 120   |

| <ul><li>7.2 I<sup>2</sup>C on the SparkFun Qwiic Bus</li></ul>                  | 123   |

| 7.4 I <sup>2</sup> C on the Seeed Studio Grove Bus                              | 125   |

| 7.5 Chapter Summary                                                             | 126   |

|                                                                                 |       |

| PART III: PROGRAMMING THE I <sup>2</sup> C BU                                   | S 129 |

|                                                                                 |       |

| 8<br>ARDUINO I <sup>2</sup> C PROGRAMMING                                       | 131   |

| 8.1 Basic I <sup>2</sup> C Programming                                          | _     |

| 8.2 Basic Wire Programming                                                      |       |

| 8.2.1 Wire Utility Functions                                                    |       |

| 8.2.2 Wire Read Operations                                                      |       |

| 8.2.3 Wire Write Operations                                                     |       |

| 8.2.4 Wire Peripheral Functions                                                 | 137   |

| 8.3 Arduino I <sup>2</sup> C Write Example                                      |       |

| 8.4 Arduino I <sup>2</sup> C Read Example                                       |       |

| 8.5 Arduino I <sup>2</sup> C Peripheral Éxample                                 |       |

| 8.6 Multiple I <sup>2</sup> C Port Programming                                  |       |

| ,                                                                               |       |

| 9 RASPBERRY PI (AND LINUX) I <sup>2</sup> C PROGRAMMING                         | 147   |

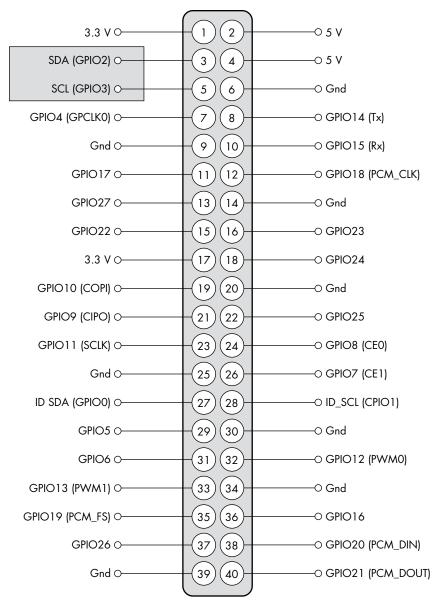

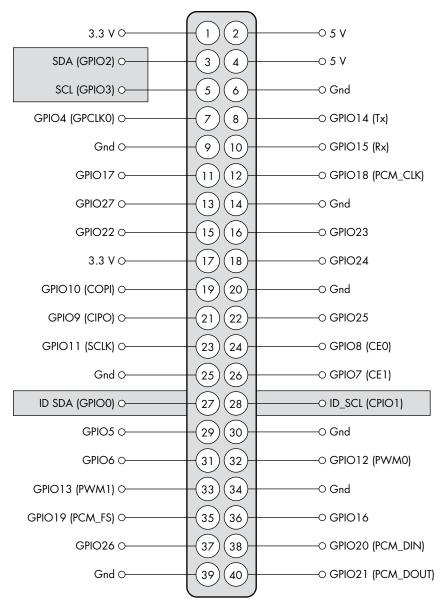

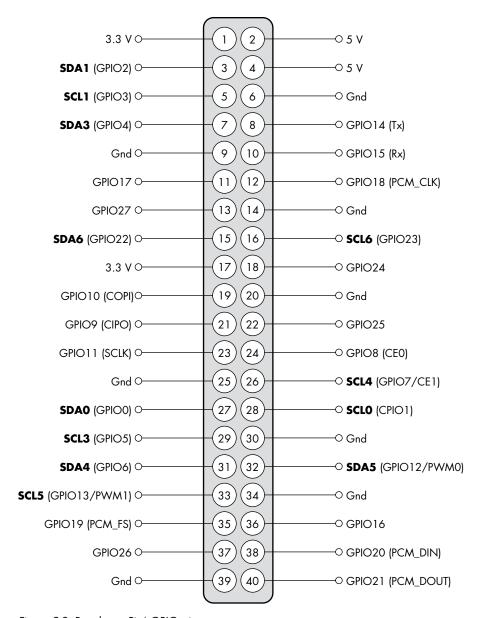

| 9.1 The I <sup>2</sup> C Bus Pins on the Pi General-Purpose Input/Output Header |       |

| 9.2 Manually Activating the I <sup>2</sup> C Buses                              |       |

| 9.3 Changing the I <sup>2</sup> C Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 9.4 I <sup>2</sup> C Clock Stretching Issues and Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 153                                                                       |

| 9.5 Raspberry Pi OS (Linux) 1 <sup>2</sup> C Utilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 154                                                                       |

| 9.6 Reading and Writing I <sup>2</sup> C Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 158                                                                       |

| 9.7 Advanced I <sup>2</sup> C Kernel Calls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

| 9.7.1 The i2c-dev Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                           |

| 9.7.2 The i2c_smbus_write_quick Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 164                                                                       |

| 9.7.3 The i2c_smbus_read_byte Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

| 9.7.4 The i2c_smbus_write_byte() Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

| 9.7.5 The i2c_smbus_read_byte_data() Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |

| 9.7.6 The i2c_smbus_write_byte_data() Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

| 9.7.7 The i2c_smbus_read_word_data() Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |

| 9.7.8 The i2c_smbus_write_word_data() Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 169                                                                       |

| 9.7.9 The i2c_smbus_read_block_data() Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 169                                                                       |

| 9.7.10 The i2c_smbus_write_block_data() Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |

| 9.7.11 Miscellaneous Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

| 9.8 Reentrancy Issues with I <sup>2</sup> C Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1/1                                                                       |

| 9.9 Multicontroller Operation Under Linux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

| 9.10 Other Linux Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                           |

| 9.10.1 PINE A64 and ROCKPro64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |

| 9.10.2 BeagleBone Black                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1/2                                                                       |

| 9.10.3 Onion Omega2+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 172                                                                       |

| 9.12 Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

| 7.12 Chapier Johnnary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1/3                                                                       |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 175                                                                       |

| 1 <sup>2</sup> C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 175                                                                       |

| I <sup>2</sup> C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS  10.1 Real-Time Operating System Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 176                                                                       |

| I <sup>2</sup> C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS  10.1 Real-Time Operating System Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 176                                                                       |

| 1°C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS         10.1 Real-Time Operating System Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 176 177 177                                                               |

| I <sup>2</sup> C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS  10.1 Real-Time Operating System Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 176<br>177<br>177                                                         |

| I <sup>2</sup> C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS  10.1 Real-Time Operating System Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 176<br>177<br>178<br>179                                                  |

| 10.1 Real-Time Operating System Basics 10.1.1 Processes and Threads 10.1.2 Multithreading and Multitasking 10.1.3 Reentrancy 10.1.4 Synchronization 10.1.5 Safety Critical Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 176<br>177<br>178<br>179<br>179                                           |

| 10.1 Real-Time Operating System Basics 10.1.1 Processes and Threads 10.1.2 Multithreading and Multitasking 10.1.3 Reentrancy 10.1.4 Synchronization 10.1.5 Safety Critical Systems 10.2 Real-Time Operating System I <sup>2</sup> C Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 176<br>177<br>178<br>179<br>179                                           |

| 10.1 Real-Time Operating System Basics 10.1.1 Processes and Threads 10.1.2 Multithreading and Multitasking 10.1.3 Reentrancy 10.1.4 Synchronization 10.1.5 Safety Critical Systems 10.2 Real-Time Operating System I <sup>2</sup> C Programming 10.2.1 µC/OS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 176<br>177<br>178<br>179<br>179<br>180                                    |

| 1°C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS         10.1 Real-Time Operating System Basics          10.1.1 Processes and Threads          10.1.2 Multithreading and Multitasking          10.1.3 Reentrancy          10.1.4 Synchronization          10.1.5 Safety Critical Systems          10.2 Real-Time Operating System I <sup>2</sup> C Programming          10.2.1 μC/OS          10.2.2 FreeRTOS I <sup>2</sup> C Programming                                                                                                                                                                                                                                                                                                            | 176<br>177<br>178<br>179<br>179<br>180<br>189                             |

| 1°C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS         10.1 Real-Time Operating System Basics          10.1.1 Processes and Threads          10.1.2 Multithreading and Multitasking          10.1.3 Reentrancy          10.1.4 Synchronization          10.1.5 Safety Critical Systems          10.2 Real-Time Operating System I <sup>2</sup> C Programming          10.2.1 μC/OS          10.2.2 FreeRTOS I <sup>2</sup> C Programming          10.2.3 Teensy Threads I <sup>2</sup> C Programming                                                                                                                                                                                                                                                | 176<br>177<br>178<br>179<br>180<br>180<br>189                             |

| 1°C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS         10.1 Real-Time Operating System Basics          10.1.1 Processes and Threads          10.1.2 Multithreading and Multitasking          10.1.3 Reentrancy          10.1.4 Synchronization          10.1.5 Safety Critical Systems          10.2 Real-Time Operating System I <sup>2</sup> C Programming          10.2.1 μC/OS          10.2.2 FreeRTOS I <sup>2</sup> C Programming          10.2.3 Teensy Threads I <sup>2</sup> C Programming          10.2.4 Mbed I <sup>2</sup> C Programming                                                                                                                                                                                              | 176<br>177<br>178<br>179<br>180<br>180<br>189<br>194                      |

| 1°C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS         10.1 Real-Time Operating System Basics          10.1.1 Processes and Threads          10.1.2 Multithreading and Multitasking          10.1.3 Reentrancy          10.1.4 Synchronization          10.1.5 Safety Critical Systems          10.2 Real-Time Operating System I <sup>2</sup> C Programming          10.2.1 μC/OS          10.2.2 FreeRTOS I <sup>2</sup> C Programming          10.2.3 Teensy Threads I <sup>2</sup> C Programming          10.2.4 Mbed I <sup>2</sup> C Programming          10.3 Other Real-Time Operating System I <sup>2</sup> C Programming                                                                                                                  | 176<br>177<br>178<br>179<br>180<br>180<br>189<br>194<br>199               |

| 1°C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS         10.1 Real-Time Operating System Basics          10.1.1 Processes and Threads          10.1.2 Multithreading and Multitasking          10.1.3 Reentrancy          10.1.4 Synchronization          10.1.5 Safety Critical Systems          10.2 Real-Time Operating System I <sup>2</sup> C Programming          10.2.1 μC/OS          10.2.2 FreeRTOS I <sup>2</sup> C Programming          10.2.3 Teensy Threads I <sup>2</sup> C Programming          10.2.4 Mbed I <sup>2</sup> C Programming                                                                                                                                                                                              | 176<br>177<br>178<br>179<br>180<br>180<br>189<br>194<br>199               |

| 1°C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS         10.1 Real-Time Operating System Basics          10.1.1 Processes and Threads          10.1.2 Multithreading and Multitasking          10.1.3 Reentrancy          10.1.4 Synchronization          10.1.5 Safety Critical Systems          10.2 Real-Time Operating System I <sup>2</sup> C Programming          10.2.1 μC/OS          10.2.2 FreeRTOS I <sup>2</sup> C Programming          10.2.3 Teensy Threads I <sup>2</sup> C Programming          10.3 Other Real-Time Operating System I <sup>2</sup> C Programming          10.4 Chapter Summary                                                                                                                                      | 176<br>177<br>178<br>179<br>180<br>180<br>189<br>194<br>199               |

| I <sup>2</sup> C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS  10.1 Real-Time Operating System Basics  10.1.1 Processes and Threads  10.1.2 Multithreading and Multitasking  10.1.3 Reentrancy  10.1.4 Synchronization  10.1.5 Safety Critical Systems  10.2 Real-Time Operating System I <sup>2</sup> C Programming  10.2.1 μC/OS  10.2.2 FreeRTOS I <sup>2</sup> C Programming  10.2.3 Teensy Threads I <sup>2</sup> C Programming  10.2.4 Mbed I <sup>2</sup> C Programming  10.3 Other Real-Time Operating System I <sup>2</sup> C Programming  10.4 Chapter Summary                                                                                                                                                                              | 176<br>177<br>178<br>179<br>180<br>180<br>189<br>194<br>199               |

| I <sup>2</sup> C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS  10.1 Real-Time Operating System Basics  10.1.1 Processes and Threads  10.1.2 Multithreading and Multitasking  10.1.3 Reentrancy  10.1.4 Synchronization  10.1.5 Safety Critical Systems  10.2 Real-Time Operating System I <sup>2</sup> C Programming  10.2.1 μC/OS  10.2.2 FreeRTOS I <sup>2</sup> C Programming  10.2.3 Teensy Threads I <sup>2</sup> C Programming  10.2.4 Mbed I <sup>2</sup> C Programming  10.3 Other Real-Time Operating System I <sup>2</sup> C Programming  10.4 Chapter Summary  11  BARE-METAL I <sup>2</sup> C CONTROLLER PROGRAMMING                                                                                                                      | 176<br>177<br>178<br>179<br>180<br>180<br>184<br>194<br>199<br>203<br>204 |

| I <sup>2</sup> C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS  10.1 Real-Time Operating System Basics  10.1.1 Processes and Threads  10.1.2 Multithreading and Multitasking  10.1.3 Reentrancy  10.1.4 Synchronization  10.1.5 Safety Critical Systems  10.2 Real-Time Operating System I <sup>2</sup> C Programming  10.2.1 μC/OS  10.2.2 FreeRTOS I <sup>2</sup> C Programming  10.2.3 Teensy Threads I <sup>2</sup> C Programming  10.2.4 Mbed I <sup>2</sup> C Programming  10.3 Other Real-Time Operating System I <sup>2</sup> C Programming  10.4 Chapter Summary  11  BARE-METAL I <sup>2</sup> C CONTROLLER PROGRAMMING                                                                                                                      | 176<br>177<br>178<br>179<br>180<br>180<br>184<br>194<br>199<br>203<br>204 |

| 10.1 Real-Time Operating System Basics  10.1.1 Processes and Threads  10.1.2 Multithreading and Multitasking  10.1.3 Reentrancy  10.1.4 Synchronization  10.1.5 Safety Critical Systems  10.2 Real-Time Operating System I <sup>2</sup> C Programming  10.2.1 μC/OS  10.2.2 FreeRTOS I <sup>2</sup> C Programming  10.2.3 Teensy Threads I <sup>2</sup> C Programming  10.2.4 Mbed I <sup>2</sup> C Programming  10.3 Other Real-Time Operating System I <sup>2</sup> C Programming  10.4 Chapter Summary  11  BARE-METAL I <sup>2</sup> C CONTROLLER PROGRAMMING                                                                                                                                                                                   | 176<br>177<br>178<br>179<br>180<br>189<br>194<br>199<br>203<br>204        |

| 10.1 Real-Time Operating System Basics  10.1.1 Processes and Threads  10.1.2 Multithreading and Multitasking.  10.1.3 Reentrancy.  10.1.4 Synchronization  10.1.5 Safety Critical Systems  10.2 Real-Time Operating System I <sup>2</sup> C Programming  10.2.1 µC/OS  10.2.2 FreeRTOS I <sup>2</sup> C Programming  10.2.3 Teensy Threads I <sup>2</sup> C Programming  10.2.4 Mbed I <sup>2</sup> C Programming  10.3 Other Real-Time Operating System I <sup>2</sup> C Programming  10.4 Chapter Summary  11  BARE-METAL I <sup>2</sup> C CONTROLLER PROGRAMMING  11.1 Teensy 4.x Controller Programming  11.1.1 i.MX RT1062 I <sup>2</sup> C Registers  11.1.2 Teensy 4.x Wire Code                                                             | 176 177 178 179 180 189 194 199 203 204  207 208 209 215                  |

| I <sup>2</sup> C PROGRAMMING IN REAL-TIME OPERATING SYSTEMS  10.1 Real-Time Operating System Basics  10.1.1 Processes and Threads  10.1.2 Multithreading and Multitasking.  10.1.3 Reentrancy  10.1.4 Synchronization  10.1.5 Safety Critical Systems  10.2 Real-Time Operating System I <sup>2</sup> C Programming  10.2.1 μC/OS  10.2.2 FreeRTOS I <sup>2</sup> C Programming  10.2.3 Teensy Threads I <sup>2</sup> C Programming  10.2.4 Mbed I <sup>2</sup> C Programming  10.3 Other Real-Time Operating System I <sup>2</sup> C Programming  10.4 Chapter Summary  11  BARE-METAL I <sup>2</sup> C CONTROLLER PROGRAMMING  11.1 Teensy 4.x Controller Programming  11.1.1 i.MX RT1062 I <sup>2</sup> C Registers  11.1.2 Teensy 4.x Wire Code | 176 177 178 179 180 189 194 199 203 204  207 208 209 215 234              |

| 10.1 Real-Time Operating System Basics  10.1.1 Processes and Threads  10.1.2 Multithreading and Multitasking.  10.1.3 Reentrancy.  10.1.4 Synchronization  10.1.5 Safety Critical Systems  10.2 Real-Time Operating System I <sup>2</sup> C Programming  10.2.1 µC/OS  10.2.2 FreeRTOS I <sup>2</sup> C Programming  10.2.3 Teensy Threads I <sup>2</sup> C Programming  10.2.4 Mbed I <sup>2</sup> C Programming  10.3 Other Real-Time Operating System I <sup>2</sup> C Programming  10.4 Chapter Summary  11  BARE-METAL I <sup>2</sup> C CONTROLLER PROGRAMMING  11.1 Teensy 4.x Controller Programming  11.1.1 i.MX RT1062 I <sup>2</sup> C Registers  11.1.2 Teensy 4.x Wire Code                                                             | 176 177 178 179 180 189 194 199 203 204  207 208 209 215 234              |

| PART IV: I <sup>2</sup> C PERIPHERAL PROGRAMMING EXAMPLES        | 251    |

|------------------------------------------------------------------|--------|

| 12                                                               | 052    |

| THE TCA9548A I <sup>2</sup> C BUS EXPANDER                       | 253    |

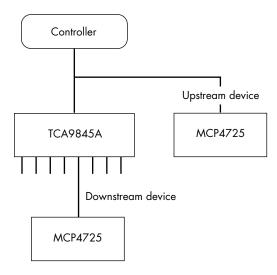

| 12.1 The TCA9548A I <sup>2</sup> C Multiplexer                   | 254    |

| 12.1.1 Upstream and Downstream Devices                           | 254    |

| 12.1.2 The TCA9548A Selection Register                           | 255    |

| 12.1.3 TCA9348A Address and Reservines                           |        |

| 12.1.5 Reducing Bus Loading and Bus Speed                        | 256    |

| 12.1.6 Switching Between Buses                                   |        |

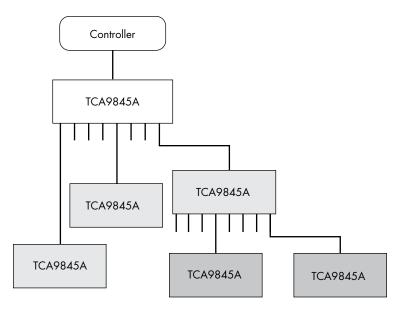

| 12.1.7 Cascading TCA9548A Multiplexers                           |        |

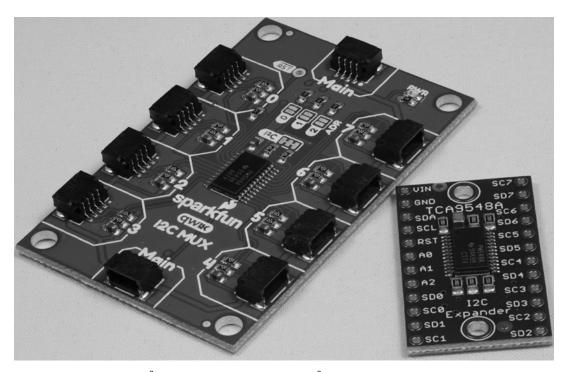

| 12.2 The Adafruit TCA9548A I <sup>2</sup> C Expander             | 258    |

| 12.3 The SparkFun I <sup>2</sup> C Mux                           | 259    |

| 12.4 Chapter Summary                                             | 260    |

| 13                                                               |        |

| THE MCP23017 AND MCP23008 GPIO EXPANDERS                         | 261    |

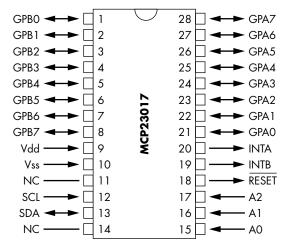

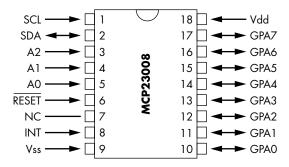

| 13.1 The MCP23017 and MCP23008 Pinouts                           |        |

| 13.2 MCP230xx Registers                                          | 264    |

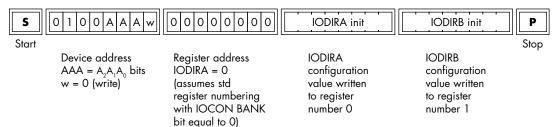

| 13.2.1 Accessing MCP230xx Registers                              |        |

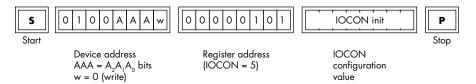

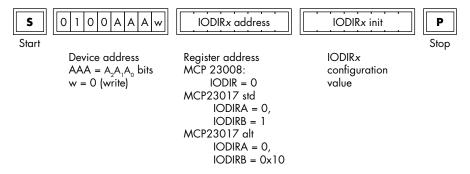

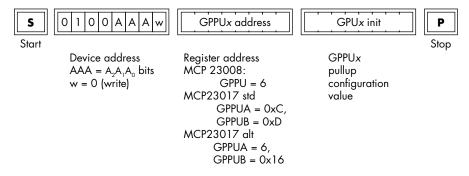

| 13.2.2 MCP230xx Initialization                                   |        |

| 13.2.3 Programming the Data Direction                            |        |

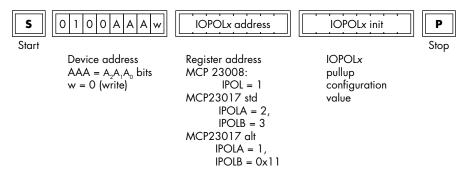

| 13.2.5 Programming the Input Polarity                            |        |

| 13.2.6 Sequential Register Operations                            | 271    |

| 13.2.7 Slew Rate Control                                         |        |

| 13.2.8 Reading General-Purpose Input/Output Pins on the MCP230xx | 274    |

| 13.3 Writing General-Purpose Input/Output Pins on the MCP230xx   | 275    |

| 13.4 Demonstrating Input/Output on an MCP23017                   | 276    |

| 13.5 Interrupts on the MCP230xx                                  |        |

| 13.5.1 Interrupt Actions on the MCP230xx                         |        |

| 13.5.2 Interrupt Service Routines                                | 281    |

| 13.5.3 Mirroring INTx Pins (MCP23017 Only)                       |        |

| 13.5.4 Open-Drain INTx Output                                    | 203    |

| 13.5.6 Testing and Clearing Interrupts                           |        |

| 13.6 A Sample Interrupt-Driven MCP230xx                          |        |

| 13.7 MCP230xx Library Code                                       | 295    |

| 13.8 I <sup>2</sup> C Performance                                |        |

| 13.9 MCP23Sxx Parts                                              |        |

| 13.10 Chapter Summary                                            | 296    |

| 14                                                               |        |

| THE ADS1015 AND ADS1115 ANALOG-TO-DIGITAL CONVERTED              | RS 299 |

| 14.1 Analog-to-Digital Converter Specifications                  | 300    |

| 14.1.1 Analog-to-Digital Converter Resolution                    | 301    |

| 14.1.2 Analog-to-Digital Converter Channel Count                 |        |

| 14.1.3 Analog-to-Digital Converter Polarity                      | 302    |

|                                                      | . 302                                          |

|------------------------------------------------------|------------------------------------------------|

| 14.1.5 Differential vs. Single-Ended Modes           |                                                |

| 14.1.6 Sample Frequency                              | . 304                                          |

| 14.1.7 Miscellaneous ADS1x15 Features                |                                                |

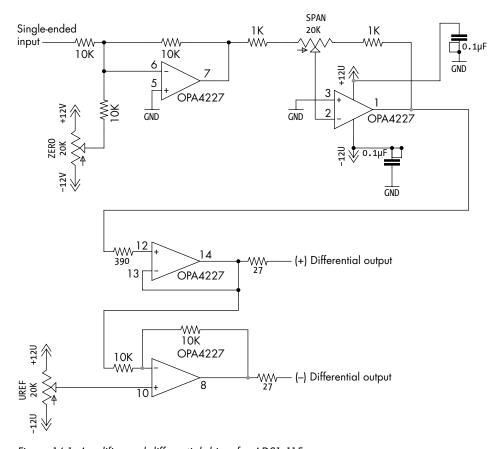

| 14.2 Analog Conditioning                             |                                                |

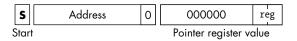

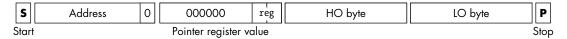

| 14.3 ADS1x15 Analog-to-Digital Converter Registers   |                                                |

| 14.3.1 The Conversion Register                       |                                                |

| 14.3.2 The Configuration Register                    |                                                |

| 14.3.3 The Low and High Threshold Registers          |                                                |

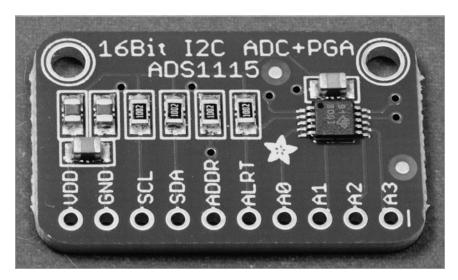

| 14.4 The Adafruit ADS1x15 Breakout Boards            |                                                |

| 14.5 An ADS1x15 Programming Example                  |                                                |

| 14.6 Improving Polling Performance                   |                                                |

| 14.7 Improving Performance Using Continuous Scanning | 220                                            |

| 14.9 Filtering Noise                                 |                                                |

| 14.9.1 Computing Means and Medians                   |                                                |

| 14.10 Chapter Summary                                | . 331                                          |

| 14.10 Chapier Summary                                | . 550                                          |

| 15                                                   |                                                |

| THE MCP4725 DIGITAL-TO-ANALOG CONVERTER              | 341                                            |

|                                                      | _                                              |

| 15.1 MCP4275 Overview                                |                                                |

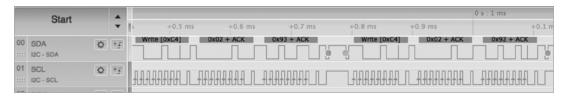

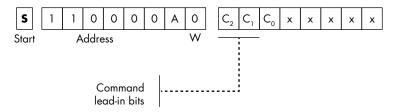

| 15.2 The Fast Write Command                          |                                                |

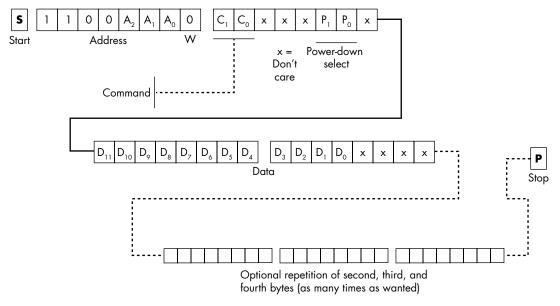

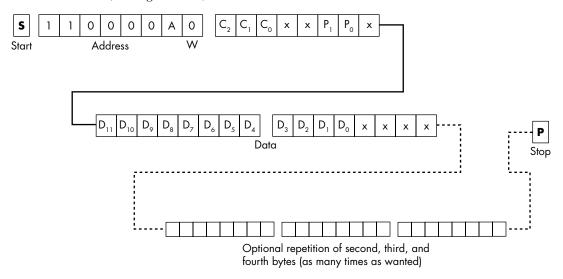

| 15.3 The Write Command                               |                                                |

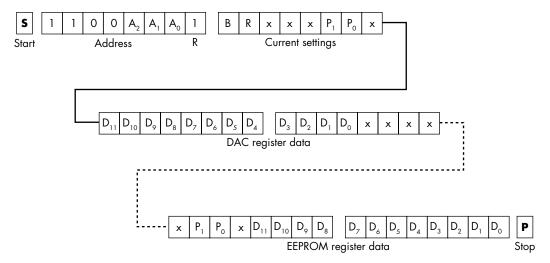

| 15.5 The Read Command                                |                                                |

| 15.6 Chapter Summary                                 |                                                |

| 13.0 Chapter Summary                                 | . 54/                                          |

| 16                                                   |                                                |

| BARE-METAL PERIPHERAL PROGRAMMING                    | 349                                            |

| <u>.</u>                                             |                                                |

| 16.1 The ATtiny as an I <sup>2</sup> C Peripheral    |                                                |

| 16.2 Introducing the Memory Peripheral               | . 351                                          |

|                                                      | . 353                                          |

| 16.3 The Memory Peripheral Software Architecture     |                                                |

| 16.3.1 The Main File                                 | . 354                                          |

| 16.3.1 The Main File                                 | . 354<br>. 359                                 |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380                        |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380                        |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380<br>. 381               |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380                        |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380<br>. 381               |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380<br>. 381               |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380<br>. 381               |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380<br>. 381               |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380<br>. 381<br><b>383</b> |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380<br>. 381               |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380<br>. 381<br>383<br>385 |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380<br>. 381<br><b>383</b> |

| 16.3.1 The Main File                                 | . 354<br>. 359<br>. 380<br>. 381<br>383<br>385 |

# **ACKNOWLEDGMENTS**

I would like to briefly mention the people at No Starch Press who made this book possible: Abigail Schott-Rosenfield, Athabasca Witschi, Jill Franklin, Bill Pollock, the production team, and anyone else I've missed.

I would also like to thank Anthony Tribelli for the great job he did as the technical reviewer for this book. The amount of effort he put into searching through datasheets, reviewing code, writing sample programs to test the book's concepts, and otherwise ensuring this book was of the highest technical quality was amazing.

I would like to thank Adafruit and Limor "Lady Ada" Fried for allowing me to use the Adafruit  $I^2C$  Address Compilation. This is an incredible resource for  $I^2C$  programmers, and its presence in this book is no small asset.

Finally, I would like to mention No Starch Press's original *The Book of SCSI: The Adventure Begins* by David Deming (2nd edition by Field, Ridge, et al.), the inspiration for this book's title.

### INTRODUCTION

Welcome to *The Book of I<sup>2</sup>C*. This book provides the resources you need to design and program systems using the Inter-Integrated Circuit Bus (IIC, I2C, or I<sup>2</sup>C), a serial protocol for connecting various integrated circuits (ICs) together in computer systems. This book will teach you how to expand your embedded system design by adding I<sup>2</sup>C peripherals with minimal wiring and software.

To paraphrase from https://i2c.info, I<sup>2</sup>C uses only two wires to easily connect devices such as microcontrollers, A/D and D/A converters, digital I/O, memory, and many others, together in an embedded system. Although it was originally developed by Philips (now NXP Semiconductors), most major IC manufacturers now support I<sup>2</sup>C. I<sup>2</sup>C is popular because it is ubiquitous—most CPUs destined for embedded systems include support for I<sup>2</sup>C—and its peripheral ICs are inexpensive. It is present in hobbyist systems like Arduino and Raspberry Pi, as well as in most professional single-board computers (SBCs) intended for use in embedded systems.

The I<sup>2</sup>C bus is especially important on hobbyist-level embedded systems employed by "makers" working on personal projects, which typically use a commercially available off-the-shelf (COTS) SBC like an Arduino Uno, Teensy 4.x, or Raspberry Pi as the brains for the system. Such SBCs generally have limited I/O capability or other limitations, so the addition of peripheral ICs may be necessary to realize a given design. The I<sup>2</sup>C bus is one of the most popular and common ways to expand such systems, since it's easy, convenient, and inexpensive to use. Furthermore, there are hundreds of different devices available as individual ICs with a wide range of capabilities that connect directly to the I<sup>2</sup>C bus. Combined with a huge library of open source code to control these devices (especially for Arduino devices), it's almost trivial to expand small systems using the I<sup>2</sup>C bus.

NOTE

The SPI bus is another popular option for hobbyist systems, but discussing it will have to wait for a different book.

Although higher-end custom SBCs intended for professional embedded systems often include many of the peripherals missing in hobbyist-grade SBCs, the I<sup>2</sup>C bus is still a cost-effective way to design such systems. Often, peripherals that don't have high-performance requirements connect to the CPU on the SBC using the I<sup>2</sup>C bus.

Because of the ubiquity of the I<sup>2</sup>C, it is difficult to work on embedded systems these days without at least a passing familiarity with the I<sup>2</sup>C bus. Sadly, most programmers are expected to figure out how to use the I<sup>2</sup>C bus on their own by searching the internet and piecing together design and programming information. This book rectifies that situation, collecting into one comprehensive book the resources needed to fully understand how to design and program systems using the I<sup>2</sup>C bus.

# **Expectations and Prerequisites**

Working with I<sup>2</sup>C peripherals requires some hardware and software expertise. In theory, an electrical engineer with no software experience could design some hardware and hand it off to a software engineer with no hardware experience, and the two of them could get something working. However, this book is not intended to be read by such teams. Rather, it's meant for software engineers who aren't afraid to get their hands dirty by working directly with the hardware, or for hardware engineers who aren't afraid to sit down with a text editor and write software.

The Book of I<sup>2</sup>C assumes you are capable of reading schematics and wiring a COTS SBC (such as an Arduino, Pi, or other commercially available SBC) to various peripheral devices using breadboarding or point-to-point wiring on prototyping boards. You should be comfortable using tools such as DVMs, oscilloscopes, logic analyzers, and more to examine and debug such circuits.

This book also assumes you are familiar with the C/C++ programming language and are capable of creating, testing, and debugging decent-sized

programs on the aforementioned SBCs. Although I<sup>2</sup>C code can be written in many different languages (including assembly language, Java, and Python), C/C++ is the universal language for embedded systems. Almost every COTS SBC's development software supports using C/C++, so the book assumes prior knowledge of this language.

Most of the examples in this book use the Arduino library due to its widespread use and simplicity. Therefore, it assumes at least a passing familiarity with the Arduino system. The Raspberry Pi examples obviously use the Raspberry Pi OS (Linux) and the Pi OS  $\rm I^2C$  library code; the book provides links to the documentation for those libraries as appropriate. For other systems (for example,  $\mu C/OS$  running on a NetBurner module or MBED running on an STM32 module), this book assumes no prior knowledge and provides either the necessary information or links to the associated documentation.

The software tools for embedded system programming generally run on Windows, macOS, or Linux. You should be familiar with the particular system running these tools (for example, the C/C++ compilers) and capable of running those tools on your own system, including learning how to use, install, and configure those tools with their accompanying documentation. As necessary, this book will describe how to find those tools and their documentation; however, its focus is the I<sup>2</sup>C bus, not running C/C++ compilers and integrated development environments (IDEs), so it leaves you to learn more about tools on your own.

### Source Code in This Book

This book contains considerable C/C++ source code that comes in one of three forms: code snippets, modules, and full-blown programs.

Code snippets are fragments of a program, provided to make a point or provide an example of some programming technique. They are not standalone, and you cannot compile them using a C/C++ compiler. Here is a typical example of a snippet:

```

while( inputPin() == 0 )

{

.

.

.

}

```

The vertical ellipses in this example denote some arbitrary code that could appear in their place.

*Modules* are small C/C++ code sections that are compilable but won't run on their own. Modules typically contain a function that some other program will call. Here is a typical example:

```

// inputPin function

int inputPin( void )

```

```

{

int p = readPort( 0x48 )

return p & 1;

}

```

Full-blown programs are called *listings* in this book, and I refer to them by listing number or filename. For example, the following example listing for an Arduino "blink" program is taken from the file *Listing1-1.ino*. The name indicates that it is the first listing in Chapter 1, and I refer to it as Listing 1-1 in the surrounding text, labeling the code itself with the filename in the comments:

```

// Listing1-1.ino

//

// An Arduino "Blink" program.

int led = 13;

void setup()

{

pinMode( led, OUTPUT );

}

void loop()

{

digitalWrite( led, HIGH ); // Turn on the LED

delay( 500 ); // Wait for 1/2 second

digitalWrite( led, LOW ); // Turn off the LED

delay( 500 ); // Wait for a second

}

```

Note that the *Listing1-1.ino* filename format applies only to code of my own making. Any other source code retains its original filename. For example, I refer to Chapter 16's code from the TinyWire library as *attiny84\_Periph.ino*. Certain non-Arduino systems (Pi OS and MBED, for example) use a standard *main.cpp* filename for their main programs; this book will generally place such programs in a subdirectory with a name such as *Listingx-x* and refer to that whole directory as the "listing." Many listings in this book are sufficiently long that I've broken them up into sections with text annotation between the sections. In such instances, I will place a comment such as // Listing10-1.ino (cont.) at the beginning of each section to provide continuity.

All listings and modules are available in electronic form at my website <a href="https://bookofi2c.randallhyde.com">https://bookofi2c.randallhyde.com</a>, either individually or as a ZIP file containing all the listings and other support information for this book, including errata, electronic chapters, and more.

Unless otherwise noted, all source code appearing in this book is covered under the Creative Commons 4.0 license. You may freely use that code in your own projects as per the Creative Commons license. See <a href="https://creativecommons.org/licenses/by/4.0">https://creativecommons.org/licenses/by/4.0</a> for more details.

# Typography and Pedantry

Computer books have a habit of abusing the English language, and this book is no exception. Whenever source code snippets appear in the middle of an English sentence, there is often a conflict between the grammar rules of the programming language and English. In this section, I describe my choices for differentiating syntactical rules in English versus programming languages, in addition to a few other conventions.

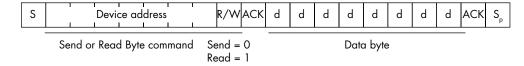

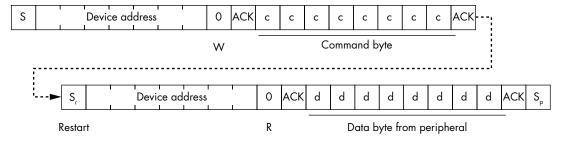

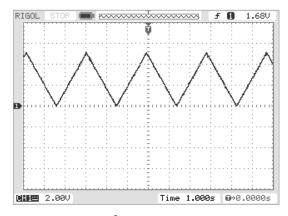

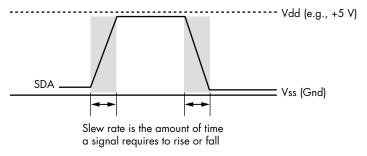

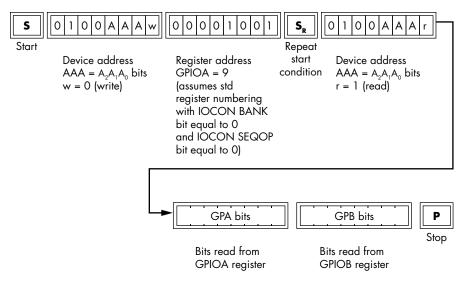

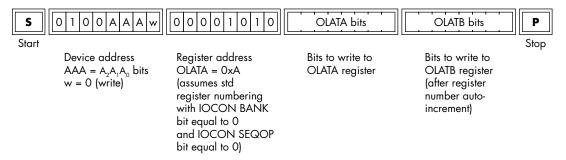

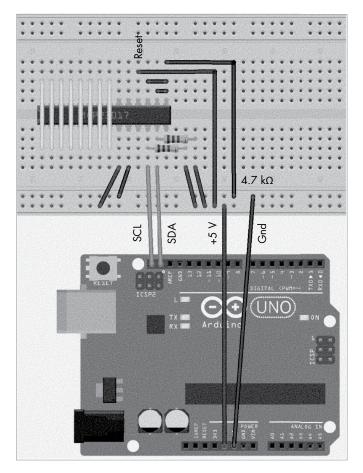

First, this book uses a monospace font to denote any text that appears as part of a program source file. This includes variable and procedure function names, program output, and user input to a program. Therefore, when you see something like get, you know that the book is describing an identifier in a program, not commanding you to get something.